低消費電力デバイス

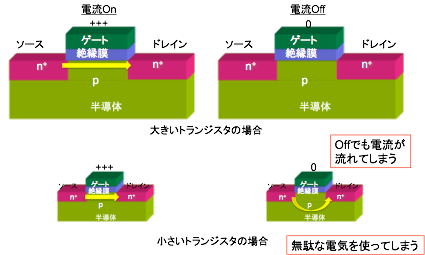

従来の集積回路に用いられたSi MOSFETでは、比例縮小によるスケーリングにより、高速動作化、低消費電力化、高集積化、低価格化が進行してきました。しかし、MOSFETの心臓部であるゲート絶縁膜の厚さが原子が数えられるほどに薄くなってしまったため、ゲート電極・ドレイン電極間で量子トンネル効果によるリーク電流が発生する問題が発生、これ以上ゲート絶縁膜を薄く出来なくなってしまいました。その結果、無理にデバイスサイズを縮小することで、ゲートオフ時にもチャンネルに電流が流れるオフステートリーク電流が発生、電力消費量が増大することとなりました。MOSFETは、元来ゲートオフ時に電流が全く流れないことで消費電力の大幅な抑制を実現したことが特徴ですので、これは致命的でした。

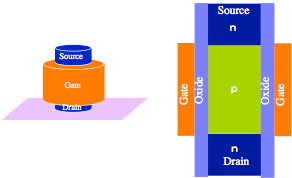

このような現象を回避するには、これまでのように片一方からのゲート電極だけでチャネル部を制御することを諦め、多方向からのゲート電極でチャネル部を制御することが考えられます。この発想から、インテルはFinFET構造を導入したのです。

しかし、平坦なプレーナー構造のままでは、集積化に限界が生じます。そこで、期待されているのが、縦型のシリコンナノワイヤを用いたFET(Vertical BC-MOSFET)です。縦型にすることで、単位面積当たりのトランジスタ集積度が格段に上昇します。また、ナノワイヤを用いるため、低消費電力化も同時に実現可能です。

一方、低消費電力化をとことん追求するためには、チャネル部分を薄層化することが良いことが知られています。しかし、SOI(シリコンオンインシュレータ)基板等を用いてシリコンを薄層化していくと、上下の界面に起因する界面散乱がキャリアの移動度を劣化させてしまいます。その一方、グラフェン等の二次元物質では、究極の薄さである単原子層であるにも関わらず、キャリアの移動度は十分に保たれ、グラフェンに至っては通常のMOSFETのシリコンを大幅に上回ります。このことから、二次元物質は、将来世代のトランジスタ材料として注目を浴びているのです。

しかし、シリコンナノワイヤデバイスや二次元物質では、トランジスタ作成の材料やプロセスに問題が山積しており、実現にはそれらの解決が必要となっています。